### **EMBEDDED COMPONENT APPLICATIONS FOR AVIONIC SYSTEMS**

Mustafa O. YÜKSELENTÜRK SDT Space & Defence Technologies Inc. ANKARA / TURKEY

#### **ABSTRACT**

Resistance to machanical shock, EMI/EMC performance, volume and weight are key parameters for avionic systems. The parameters which are given above highly depend on the capability of Integrated Circuit and Passive Component manufacturers. On the other hand, new approach for Printed Circuit Design and Component Packaging, makes it possible to reduce electronic system dimensions. New design methods also improve the key parameters of avionic systems.

#### INTRODUCTION

By applying new design methods and using Chip Scale Packaged components, avionic systems will be lighter, more reliable and undersized. Embedding the components at inner layers of PCB (Printed Circuit Board), brings the capability of 3-D integration of components and increase the PCB density of system. Formula of PCB Density is given below.

## Eqn. 1:

Cd = p/a Cc = l/p  $\beta = \sqrt{(Cd)x(Cc)}$

Where

$\beta$ =PCB Density p=Number of components l=Number of leads (I/Os) of all components a= Area of board Cd= Assembly Complexity (or Component Density) Cc= Component Complexity (the degree of sophistication of components)<sup>1</sup>

### **EMBEDDED COMPONENT APPLICATIONS**

Embedded component application is, to assemble the components at inner layers of PCB. By using this design and manufacturing method; size of electronic systems could be reduced significantly. Embedded component applications could be divided into two main groups according to components to be embed. First group is the "Passive Components". Embeddable passive components are Resistors and Capacitors. The second class is the "Active Components". In this case, all Integrated Circuits can be assembled to inner layers as Chip Scale Package form or Bare Die form.

### **Embedding Passive Components**

Embeddable passive components are manufactured as thin sheets to be laminated on FR4 base of PCB. Design and occupation decision process, is made during PCB design. According to

BSc Senior Component & PCB Design Engineer; at SDT Space & Defence Technologies Inc. myukselenturk@sdt.com.tr

<sup>&</sup>lt;sup>1</sup> Happy Holden, HDI HANDBOOK 1st Edition 2009 P: 50-51

desired resistance or capacitance values, special trace and component bodies should be designed.

# a) Resistor Design in PCB

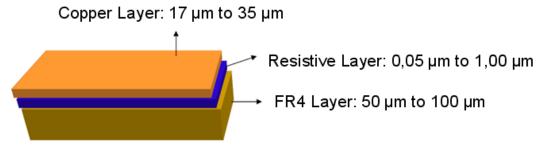

Structure of embedded resistor layer is shown below in Figure 1. Embedded resistor layer is a composition of resistive layer and copper. This composite layer shall be laminated on desired layer of PCB during fabrication.

Figure 1: Structure of Embedded Resistor Layer

Many pins of integrated circuits, require unique resistance for pull-up, pull-down or termination purposes. So designer should design the required resistor according to user reference of integrated resistor. Resistance value of an embedded resistor should be calculated according to formula given below which is driven from general formula of resistance. <sup>2</sup>

Eqn. 2:

$$R = \rho \times \frac{L}{A} \Rightarrow \rho \frac{L}{T \cdot W} \Rightarrow R_S \times \frac{LENGTHofRESISTOR}{WIDTHofRESISTOR}$$

Where

R = Total Resistance

$\rho$ = Resistivity

L=Length

A = Area

Eqn. 3:

$$R = R_s \times N$$

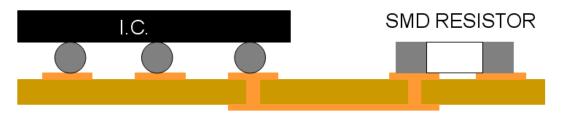

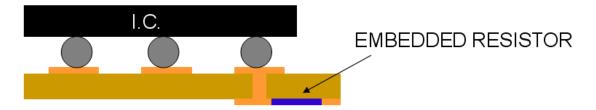

Figure 2 represents the cross section of connection for an integrated circuit and that connected to a suface mount resistor. Figure 3 represents the cross section of an integrated circuit that is connected to an embedded resistor on layer 2 of PCB. Space saving on surface area of PCB can be seen apparently.

Figure 2: Schematical Corssectional View of SMD Resistor Application

<sup>&</sup>lt;sup>2</sup> Dong NONG, Ohmega Technologies Inc. Design Tutorial p:4

Figure 3: Schematical Corssectional View of Difference Embedded Resistor

Application

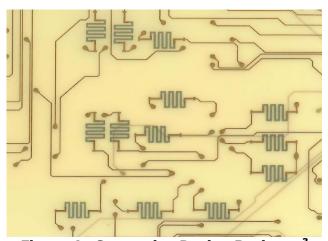

In cases of high value resistors required for an application, serpentine design is useful to save space instead of a linear resistor design. Figure 3 shows a serpentine designed high value resistor. Figure 4 represents the stright designed low valued resistor.

Figure 4 : Serpentine Design Resistors<sup>3</sup>

Figure 5: Linear Design Resistors<sup>4</sup>

# b) Capacitor Design in PCB

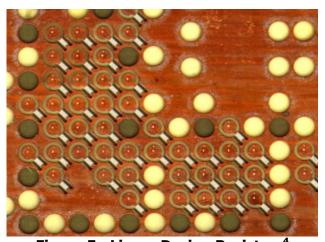

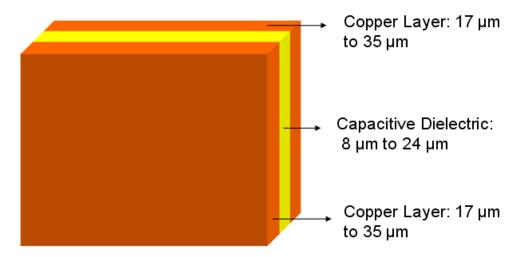

Embedded Capacitor application in PCB is easier than the resistor design. Structure of Embedded Capacitor Layer shown below Figure 4. Embedded Capacitor layer is manufactured as a sandwich that is composed of two copper layer at outside and a capacitive layer (high dielectric constant) between them.

<sup>&</sup>lt;sup>3</sup> Dong NONG, Ohmega Technologies Inc. Design Tutorial p:24

<sup>&</sup>lt;sup>4</sup> Dong NONG, Ohmega Technologies Inc. Design Tutorial p:22

**Figure 6: Structure of Embedded Capacitive Layer**

According to capacitance theory, the capacitance between two metal plates directly proportional to Area of Plates and Dielectric Constant. On the other hand capacitance is inversely proportional to distance between plates. The capacitance formula can be written as in below.

Eqn. 3:  $C = \frac{A \times D_k \times K}{d}$

C : Capacitance

$D_k$ : Dielectric Constant

K : Constantd : Distance

One metal layer of Embedded Capacitor is determined as Voltage plane and the other one is Ground. So the remaining area of Voltage Plane and Ground Plane can be calculated as, subtract the via hole antipads from the area of board outline. The other parameters are definitely constant. Finally; in practice, the total capacitance directly depends on the total area of the voltage and ground planes.

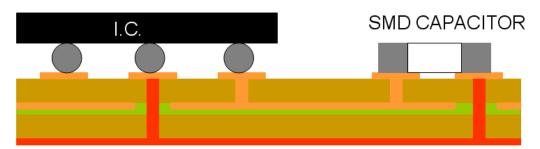

Figure 6: Schematical Corssectional View of Difference Between SMD and Embedded Capacitor Application

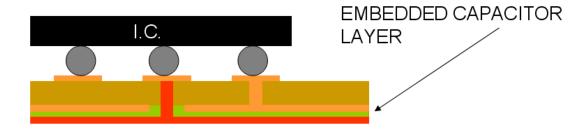

Figure 7: Schematical Corssectional View of Difference Between SMD and Embedded Capacitor Application

## **Embedding Active Components**

Embedding process of active components or integrated circuits is different, when compared to passives. In order to embed an integrated circuit, PCB assembler should have the Bare Die or Chip Scale Package (CSP) form of integrated circuits (IC). The reason for using Bare Die or CSP of ICs is the small mechanical dimensions. The dimensions of a CSP of an integrated circuit generally less than 20mm X 20 mm x 1,0 mm. According to J-STD-012; Bare Die form is 20% smaller than the CSP. However the soldering process of Bare Die, requires additional process steps. So the optimum way is to embedding the CSP for lower cost.

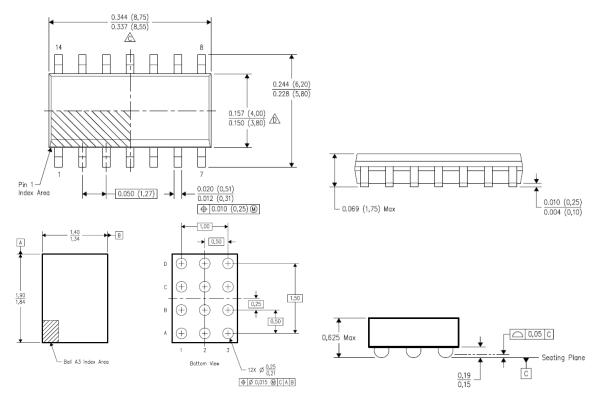

Forexample, in order to compare and realize the dimension difference between conventional package dimensions and CSP dimensions, Texas Instruments TXS0104E is choosen. SOIC package of TXS0104E and Die Size Ball Grid Array version drawings are given in below. It is obvious, the surface area of DSBGA is 1,40x1,90=2,66mm<sup>2</sup> and area of the SOIC package is 4,00x8,75=35mm<sup>2</sup>. In the case of using DSBGA form of IC, the residental area shrink 13 times, after embedding process a 3-D stack of components became applicable.

Figure 8: SOIC and DSBGA Package Dimensions of Texas Instruments TXS0104E

At the design level, PCB designer should determine the suitable layer and than design the pads at inner side of PCB. During the fabrication, at multilayer lamination step; IC should be attached to the pads, than upper layer are laminated on IC.

Figure 9: Schematical Representation of Embedding ICs.

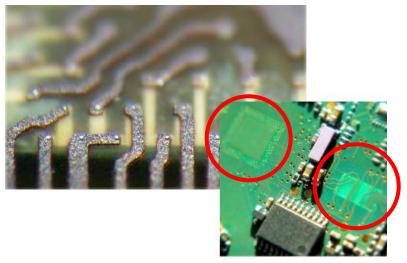

There are many benefits of embedding active components application. Most common usage of embedding process is to miniaturize the PCB, increase the EMI/EMC and Mechanical Shock/Vibration performance. These benefits lead to growth of application areas also in avionics.

Figure 10: Embedded IC Application by Imberra Inc.<sup>5</sup>

## **Applications in SDT**

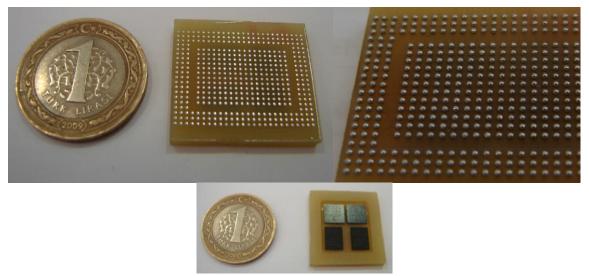

Another application is the Multi Chip Module design. In this case of application, the modules that would solve the generic needs of system designers at module level such as a generic memory module or a generic secure communication module. A generic memory module which designed and manufactured at Integration Laboratories of SDT Space & Defence Technologies Inc. shown below. The module include memory ICs and driver ICs at the core, than the signal, ground and voltage connections connected the solder balls at the bottom. In this case the module could be solderable as an ordinary Ball Grid Array Integrated Circuit.

6

<sup>&</sup>lt;sup>5</sup> Risto TUOMINEN, Embedded Components in PCB, 09/2008 P:15

Figure 11: Generic Memory Module Draft Design

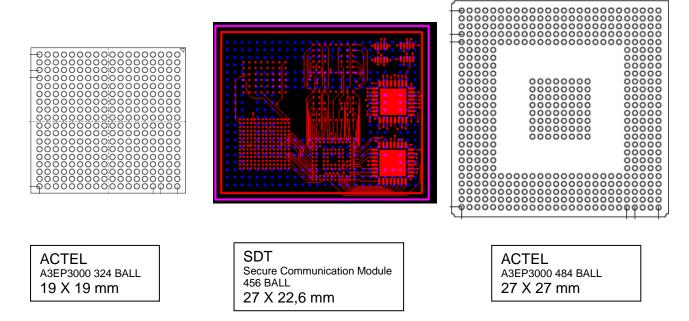

As another draft design, a generic Secure Communication Module is significant application for embedded integrated circuit application. It includes 1 FPGA, 1 PROM, 2 SRAM, 1 Microprocessor, 2 Random Number Generators, 2 Power ICs. Final dimensions of Secure Communication Module is smaller than an ordinary FG484 package FPGA. Because of this property of Module, it is highly useful in communication devices and also for missile applications.

Figure 12: Secure Communication Module Draft Design

### **CONCLUSIONS**

As a result of design and assembly experience, Embedded Passive and Embedded Active Applications capability is redounded. Through this capability, it is possible to reduce the dimensions of avionic systems and sub-systems significantly. Smart missile applications and Small UAV platforms are the target possible projects of this applications. On the other hand, this process increase the reliability of systems and resistance to mechanical shock of avionic systems. Through this property, it is possible to manufacture more reliable avionic equipments for highly vibrating rotary wing aircrafts.

### **REFERENCES**

- [1] IPC-2316 Design Guide for Embedded Passive Device Printed Boards , Institute for Interconnecting & Packaging Electronic Circuits, March 2007.

- [2] IPC-4811 Specification For Embedded Passive Device Resistor Materials for Rigid and Multilayer Boards, Institute for Interconnecting & Packaging Electronic Circuits, April 2008.

- [3] IPC-4821 Specification For Embedded Passive Device Capacitive Materials for Rigid and Multilayer Boards, Institute for Interconnecting & Packaging Electronic Circuits, May 2006.

- [4] IPC-6017 Qualification and Quality Specification For Printed Boards Containing Embedded Passive Devices, Institute for Interconnecting & Packaging Electronic Circuits, March 2009.

- [6] HOLDEN H., ANDRESAKIS J., BOGATIN E., CARANO M., CARPENTER C., DIETZ K., LAING M., VAUCHER C., VIKLUND P., WUENSCH M., The HDI Handbook, 2009.

- [7] Tummala R., Swaminathan M., System on Package Miniaturization of the Entire System 2008.

- [8] IPC-7094 Design and Assembly Process Implementation for Flip Chip and Die Size Components, Institute for Interconnecting & Packaging Electronic Circuits, February 2009.

- [9] IPC-J-STD-028 Performance Standard for Construction of Flip Chip and Chip Scale Bumps Institute for Interconnecting & Packaging Electronic Circuits, August 1999.

- [10] IPC-6016 Qualification and Performance Specification for High Density Interconnect (HDI) Layers or Boards, Institute for Interconnecting & Packaging Electronic Circuits,

- [11] TUOMINEN Risto, Embedded Components in PCB, 09/2008 P:15

- [12] 4-BIT Bi-Directional Voltage-Level Translator for Open-Drain and Push-Pull Applications, Rev May 2008, Texas Intruments Inc.